8 Bit Parallel In Serial Out Shift Register Vhdl Code

- Parallel In Serial Out Shift Register

- Parallel-in Serial-out Right-shift Register

- 8 Bit Parallel In Serial Out Shift Register Verilog Code

Logic levels, zeros and ones. A shift register has the capability of shifting the data stored in the register from left to right or right to left. Shift registers consist of D flip-flops as shown in the figure below. This is a four bit shift register and therefore consists of four D flip-flops. This shift register is configured to shift data from the left to the right.

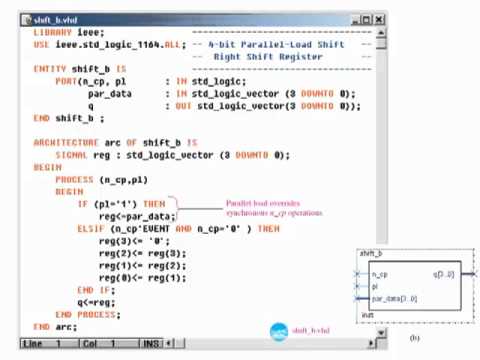

Simpreg.vhd simpreg Simple 8 Bit Register 4. Implements a simple parallel-serial converter- with load and shift. 8-bit parallel to serial converter in VHDL.

Nov 12, 2013 Hi guys this is my first post. In my programme i have to Design a Serial In, Parallel Out, (SIPO) sift register with a Clock and Data input (both single lines and an 8-bit parallel output Q. Serial data is accepted at the shift register input on a rising clock edge and is placed in the least significant bit – the other 7 bits of existing data. I'm creating an n bit shift register. N bit shift register (Serial in Serial out) in VHDL. Shift register parallel in serial out.

Parallel In Serial Out Shift Register

I'm creating an n bit shift register. When the enable signal is high, I want the shift register to shift n times, irrespective of whether enable continues to be high or low.

Pins P3 to P7 are understood to have the smae internal 2,3 prefix labels as P2 and P8. At SER, the 1,3D prefix implies that M1 and clock C3 are necessary to input serial data. Right shifting takes place when M1 active is as indicated by the 1 in C3/1 arrow. The CD4021B is a similar part except for asynchronous parallel loading of data as implied by the lack of any 2 prefix in the data label 1D for pins P1, P2, to P8. Of course, prefix 2 in label 2D at input SER says that data is clocked into this pin. The OR gate inset shows that the clock is controlled by LD/SH’. The above SN74LS674 internal label SRG 16 indicates 16-bit shift register.

A shift register is written in VHDL and implemented on a Xilinx CPLD. Two different ways to code a shift register in VHDL are shown. Shift Register Operation A register stores data i.e. Logic levels, zeros and ones. A shift register has the capability of shifting the data stored in the register from left to right or right to left. Shift registers consist of D flip-flops as shown in the figure below. This is a four bit shift register and therefore consists of four D flip-flops.

Second, whenever M1 is asserted, as indicated by the 1 of C3/1 (arrow), the data is shifted as indicated by the right pointing arrow. The slash (/) is a separator between these two functions. The 8-shift stages, as indicated by title SRG8, are identified by the external inputs A, B, C, to H. The internal 2, 3D indicates that data, D, is controlled by M2 [Load] and C3 clock.

This register is initialized with the value of 00h so that when power is switched on to the CPLD board, the register will be cleared. The shift_reg register is 8 bits wide and the VHDL code connects each bit in the register to an LED, so that 8 LEDs show the value in each bit of the register. On the, the LEDs will all initially be switched on because of the wiring of the LEDs to the CPLD which effectively inverts the logic level on the CPLD pin. Library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity shift_register_top is Port ( CLK: in STD_LOGIC; D: in STD_LOGIC; LED: out STD_LOGIC_VECTOR(7 downto 0)); end shift_register_top; architecture Behavioral of shift_register_top is signal clock_div: STD_LOGIC_VECTOR(4 downto 0); signal shift_reg: STD_LOGIC_VECTOR(7 downto 0):= X'00'; begin -- clock divider process (CLK) begin if (CLK'event and CLK = '1') then clock_div.

Any switch closures will apply logic 0s to the corresponding parallel inputs. The data pattern at P1-P7 will be parallel loaded by the LD/SH’=1 generated by the microprocessor software. The microprocessor generates shift pulses and reads a data bit for each of the 8-bits. This process may be performed totally with software, or larger microprocessors may have one or more serial interfaces to do the task more quickly with hardware. With LD/SH’=0, the microprocessor generates a 0 to 1 transition on the Shift clock line, then reads a data bit on the Serial data in line. This is repeated for all 8-bits.

On the, the LEDs will all initially be switched on because of the wiring of the LEDs to the CPLD which effectively inverts the logic level on the CPLD pin. Library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity shift_register_top is Port ( CLK: in STD_LOGIC; D: in STD_LOGIC; LED: out STD_LOGIC_VECTOR(7 downto 0)); end shift_register_top; architecture Behavioral of shift_register_top is signal clock_div: STD_LOGIC_VECTOR(4 downto 0); signal shift_reg: STD_LOGIC_VECTOR(7 downto 0):= X'00'; begin -- clock divider process (CLK) begin if (CLK'event and CLK = '1') then clock_div.

The last stage (Q D above) serves as SO and is cascaded to the next package if it exists. Serial-in, Parallel-out vs. Serial-in, Serial-out Shift Register If a serial-in, parallel-out shift register is so similar to a serial-in, serial-out shift register, why do manufacturers bother to offer both types? Why not just offer the serial-in, parallel-out shift register? The answer is that they actually only offer the serial-in, parallel-out shift register, as long as it has no more than 8-bits. Note that serial-in, serial-out shift registers come in bigger than 8-bit lengths of 18 to 64-bits.

Field service and parts for Airco Temescal electron beam gun power supplies, electron beam guns, electron beam sweeps,deposition systems and helium leak detectors. Field service and parts for Airco Temescal electron beam gun power supplies, electron beam guns, electron beam sweeps,deposition systems and helium leak detectors. Schematics and Drawings (Adobe PDF Format required to read prints). CV-8 Manual: CV-14 Power Supply Schematics. Power Supply Control Rack Sheet 2 of 2. Airco Temescal Cv-8 Manual Karl Suss MA150 Mask Aligner with Manual Substrate Handling Temescal FC-1800 Electron Beam Evaporator Power Supply CV-8 Substrate Heaters Electron-Beam E-Gun Power Supply. Parts and service for Airco Temescal electron beam guns, power supplies and sweeps. IF YOU ARE LOOKING FOR REPLACEMENT PARTS OR. REPAIR OF TEMESCAL MODEL POWER SUPPLIES CV-8 AND CV-14. Airco temescal cv-8 manual.

Parallel-in Serial-out Right-shift Register

This is what's happening in your code. The entire loop is executing in a single clock cycle, and the value of s_out is only going to change once - to the value it was when the loop ended, which in this case is s_in shifted by 4. What you really want is a loop where each iteration occurs on a new clock edge. Font thai free download. This allows for s_in to be shifted out of s_out ever clock cycle. Performing a loop where each iteration occurs on a clock edge does not require a for loop command, instead it takes advantage of the sensitivity list of the process. Here's how: A process is triggered every time one of the signals on the sensitivity list ('clk, reset' in this case) changes. This means that the process is already looping every clock cycle (if a clock is in the sensitivity list).

Let us note the minor changes to our figure above. First of all, there are 8-stages. We only show three.

The advantage of the ANSI symbol is that the labels provide hints about how the part operates. The large notched block at the top of the ‘74ASL166 is the control section of the ANSI symbol. There is a reset indicted by R. There are three control signals: M1 (Shift), M2 (Load), and C3/1 (arrow) (inhibited clock). The clock has two functions. First, C3 for shifting parallel data wherever a prefix of 3 appears.

8 Bit Parallel In Serial Out Shift Register Verilog Code

At the end of the day HDL is just a text-based way of expressing the content of logic schematics.

VHDL code: This video is part of a series which final design is a Controlled Datapath using a structural approach. A Structural approach consist in designing all components needed for the design such as gates to form subsystems and then joining them together to form a larger design like adders and Arithmetic logic units,etc. The design in these labs was first developed in VHDL you can check the final VHDL version in the link below as well as intructions on how to set up the Waveshare development board to get started, the setup is the same for VHDL and Verilog: Lab Sheets: Lab guide The complete video tutorial at: The design in this lab covers the basics of microcontrolller structural design DONATE with PAYPAL: quitoart@hotmail.co.uk Support me through Patreon! DONATE with PAYPAL: quitoart@hotmail.co.uk Support me through Patreon! Suppoert me by accessing my blog through an Ad: DONATE with BITCOIN: 1PJJiXCLqNPuQtyRebwUHdwqNJGaZsfVGt DONATE with Ethereum: 0x4671bfa4f73a6ffc5f214cf27c921b DONATE with LiteCoin: LhKtK8KEoxdpVBJLZLbEZKjjDpeHmenAPd DONATE with ZCASH: t1Md3vXgojrk5cX6jqhFpjaTWQ1fbLGFZZg.